DDR4内存全景解析

点对点总线

如果说Bank Group是DDR 4内存带宽提升的关键技术的话,那么点对点总线则是DDR4整个存储系统的关键性设计。在传统的DDR 3等内存上,内存和内存控制器链接依靠的是多点分支总线(Multidropbus)。这种总线允许在一个接口上挂接许多同样规格的芯片。比如主板上往往为双通道设计四根内存插槽,每个通道在物理结构上只允许扩展更大容量。打个比方来说,这种设计类似于为每次只能双向通行一对汽车的道路边修建仓库,仓库直连道路,虽然每个仓库都有自己的运输车和运输能力,但道路只允许每次双向通行一对车,因此这种设计如果不停的加修仓库,只是扩大了存储能力而已,对运输能力帮助不大。

DDR 4抛弃了这样的设计,转而采用点对点总线。点对点总线的特性是:内存控制器每通道只能支持唯一的一根内存。相比多点分支总线,点对点相当于为每个仓库都设计了一条道路,有效利用了仓库本身的运输能力—换句话来说是有效利用了每个内存的位宽。点对点的优点很多,比如设计比较简单、容易达到更高的频率等。此外,之前点对点总线存在的一些问题,比如可能强制要求通道上内存容量和规格完全相同等,在当前弹性内存多通道技术的发展下,已经不太可能影响DDR4内存的使用,未来用户有很大可能依旧可以在不同的通道上配置不同规格的内存,即能节约投资又能提高性能。

说起提高性能,点对点内存对带宽的提高是极为明显的。得益于工艺的进步和点对点内存控制器相对不复杂的设计,未来民用PC中支持DDR 4的产品可能使用四通道点对点内存控制器。这就意味着内存插得越多,带宽越大、性能越强。未来的主板上依旧是四条内存插槽,但它们的分布方式可能改成左右各两条(线路等长问题),同时通道数和大带宽数都已经翻倍(4通道,256bit)。以DDR 43200计算,在4通道的情况下,可以提供约102.4GB/s(3200×64×4÷8)的带宽,远远超出目前25G B/s左右的带宽,即使是普通的双通道,带宽也高达52.2GB/s,也超出目前主流水平100%还多。

当然,点对点的优势很多,不过并不意味着十全十美。它的问题也同样明显:一个重要因素是点对点总线每通道只能支持一根内存,因此如果DDR4内存单条容量不足的话,将很难有效提升系统的内存总量。

为了解决容量难题,DDR4采用了两种办法来应对:

第一种办法是增大每根内存的容量。除了使用更先进工艺降低内存颗粒的面积、在PCB上布置更多内存芯片外,DDR4还打算在内存生产中启用堆叠芯片技术,这项技术被称为“3DS”。有关3DS技术的内容,后文还有详细的描述。

第二种办法是设置多个Digital Switch,通过这些Digital Switch挂接更多的内存来实现更大容量。Digital Switch实际上相当于一个采用了多点分支总线的内存控制器,通过在总线上挂接更多的内存来实现更高容量。只不过传统的内存控制器链接的是CPU核心,而Digital Switch链接的是点对点内存控制器。使用Digital Switch挂接4条内存的话,内存容量就可以在通道数维持不变的情况下翻两番,应该能解决用户对内存容量的需求。由于Digital Switch实现成本比较高,因此这种办法主要在服务器中采用,民用级市场上应该不太可能会出现。

叠起来,更大容量

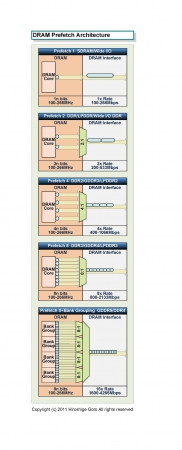

为了彻底解决单条内存容量限制,DDR4准备启用堆叠封装来增大单颗芯片的容量,这也是DDR4内存中关键的技术之一。这项技术在DDR4中被称作3DS(3-Dimensional Stack)。

堆叠技术可以大大提高芯片容量,但与此同时带来了散热等问题,DDR4在这方面应该早有准备!

堆叠封装后,DDR4多层DR A M实际上只有一个被系统控制,其余的是隐藏在背后的,只起到增大容量的作用。

实际上堆叠封装技术并不神秘,在当前就有一些类似应用。比如手机芯片中的处理器和存储器很多都采用堆叠焊接在主板上以减少体积—堆叠焊接和堆叠封装的差别在于,一个在芯片封装完成后、在PCB板上堆叠;另一个是在芯片封装之前,在芯片内部堆叠。一般来说,在散热和工艺允许的情况下,堆叠封装能够大大降低芯片面积,对产品的小型化是非常有帮助的。在DDR4上,堆叠封装主要用TSV硅穿孔的形式来实现。

所谓硅穿孔,顾名思义,就是芯片上存在很多孔洞。硅穿孔的生产方式和目前的多层PCB工艺有异曲同工之妙,多层PCB电路板生产中,为了保证PCB层间的电信号传输,在PCB上往往会开通不同类型的孔,比如埋孔、穿孔等,这些孔之间使用导线连接,使得电信号能在PCB不同的绝缘层之间传输。硅穿孔技术与之类似,它首先在硅片上钻出小孔(根据不同工艺分又为先孔和后孔,加工方式可以使用蚀刻也可以用激光打孔),然后填入金属联通孔洞。经过硅穿孔的不同硅片之间的信号可以互相传输。从宏观意义上来说,硅穿孔是晶体管布局3D化和空间化技术尚未成熟之前,减少芯片占地面积,提高晶体管密度并延缓摩尔定律的有效手段。

在DDR4中,采用硅穿孔后的多层芯片中,只有一个主DRAM,其余的都是从DRAM(多可以叠加7层,加上主DRAM共8层)。芯片在工作时,只面向主DRAM,系统就像操作单层芯片那样操控所有的堆叠芯片。从DRAM是被隐藏起来不在系统中出现的,唯一证明其存在的证据就是容量。此外,所有的芯片都使用统一的连接界面和PCB以及内存控制器相连。实际上这样的组织方式类似于“片上分支总线”,但结构设计更为简单和直接。

根据JEDEC的说明,在使用了3DS堆叠封装技术后,单条内存的容量大可以达到目前产品的8倍之多。举例来说,目前常见的大容量内存单条容量为8GB(单颗芯片512MB,共16颗),未来DDR4大可以达到64GB,甚至128GB,彻底解决了点对点总线容量不足的问题。另外,即使堆叠层数没有那么多,DDR4内存在4层堆叠的情况下也至少可以达到单条32GB,双通道64GB,基本可以满足未来三、五年左右的内存容量需求了。

稳定性设计

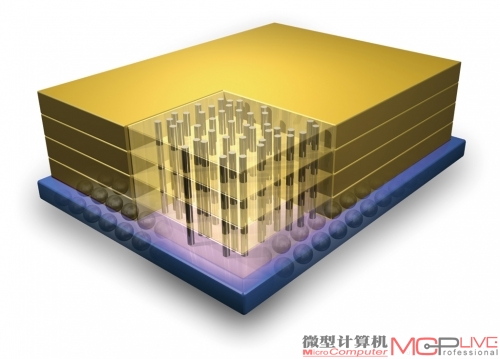

高频率、高密度等设计在带来DDR4强大性能的同时,也对DDR4本身的信号稳定性和功耗情况提出了严峻挑战。实际上,根据JEDEC的官方资料, DR4内存为重要的部分就是功耗优化,其余几个重要目标分别是性能优化、信号和可靠性优化。

首先来看功耗方面的内容。DDR4内存采用了TCSE ( Temperature Compensated Self-Refresh,温度补偿自刷新,主要用于降低存储芯片在自刷新时消耗的功率)、TCARtemperature Compensated Auto Refresh,温度补偿自动刷新,和T CSE类似)、DBI(Data Bus Inversion,数据总线倒置,用于降低VDDQ电流,降低切换操作)等新技术。这些技术能够降低DDR4内存在使用中的功耗。当然,作为新一代内存,降低功耗直接的方法是采用更新的制程以及更低的电压。目前DDR4将会使用20nm以下的工艺来制造,电压从DDR3的1.5V降低至DDR4的1.2V,移动版的SO-DIMMD DR4的电压还会降得更低。

根据一些测试资料,在同为1866MHz的等效频率、2GB容量的情况下,DDR4的总功耗大约是439毫瓦,不但低于DDR3的687毫瓦,也低于DDR3L的612毫瓦;在2133MHz的等效频率下,DDR4的功耗为488毫瓦,远远低于DDR3的763毫瓦,也比DDR3L的660毫瓦还要低很多。这说明在工艺进步、电压降低以及联合使用多种功耗控制技术的情况下,DDR4的功耗表现是非常出色的。

除了功耗外,DDR4的信号稳定性也值得重视。目前已知的DDR4采用了诸如CRC(Cyclic Redundancy Check,循环冗余校验,用于实时校验错误)、CAParity(CMD ADDRParity,CA对等,用于检查命令和地址总线是否有错)、PAD(Per DRAM Addressability,用于校验总线功能)等多种技术确保信号完整性。

总的来看,DDR4在功耗控制和信号控制技术上比较成熟,使用的都是目前已经有广泛应用的现成技术。这些技术控制了DDR4功耗、确保了信号稳定性的同时,也为DDR4能够在高频率下稳定运行立下了汗马功劳。

未来的绝对主力

DDR4既然如此优秀,那么什么时候才能用到它呢?这个问题需要分两个方面来看:

一方面是DDR4本身。根据镁光等厂商的资料,DDR4从2013年开始试生产并开始正式出货,2014年开始大面积生产。在2016年左右,DDR4将会彻底取代DDR3成为主流产品,届时DDR4的市场占有率应该超过50%(DDR3应该还有约1/3的市场占有率)。现在,用户已经可以在镁光、三星等DRAM厂商的页面上查询到有关DDR4产品的相关信息和参数了,镁光甚至已经开始销售DDR4内存颗粒。

另一方面就是平台支持情况了。目前英特尔和AMD都没有明确的信息表示将在何时开始使用DDR4。一些消息表明英特尔下一代顶级平台Haswell-EX将开始初步支持DDR4内存,不过不太清楚是独占式支持DDR4还是DDR4和DDR3都会支持。AMD方面APU应该对带宽更饥渴,DDR4的出现会让APU的性能得到巨大的提升,但目前依旧缺少AMD支持DDR4的消息。估计来看,英特尔很可能在2014年首先在新的移动平台上宣布对DDR4的支持,AMD也应该差不多在同一时间开始支持DDR4,在2015年将有希望看到DDR4产品的大爆发。

除了上市情况外,DDR4本身的发展情况也值得关注。根据镁光的路线图,DDR4内存在2013年首先推出DDR4 1866、DDR4 2133的规格,随着时间发展会在2015年延伸至DDR4 2667,在2016年还有可能更高。不过这份路线图显得较为保守,据其他方面的消息,DDR4在进入成熟期(2015年之后),很可能快速发展出高频版本,玩家级别的产品会使用到DDR4 3200乃至更高,终可以达到DDR4 4266等高规格。

总的来看,未来的DDR4发展在JEDEC标准支持以及各大DRAM厂商的护持下,肯定是一帆风顺的。AMD英特尔等平台厂商绝不会也没有理由阻碍DDR4的发展。因为DDR4将会显而易见带来PC行业的又一波升级热潮。除此之外,SO-DIMM的DDR4版本以及DDR4在移动平台上的应用都会引发新的销售和技术升级狂潮,超高带宽带来的不仅仅是更快的使用速度,对厂商来说还有更多的金钱和利润,前景完全可期。

DDR4使用了大量技术降低功耗,其中重要的就是电压调整到1.2V。

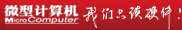

Tips:数据预取在DDR发展中的作用

内存发展到SDRAM末期,出现了RDRAM和DDR的路线之争。RDR AM的技术核心是串行,DDR的技术核心是数据预取。由于DDR在成本和专利上的优势,市场终选择了DDR。从这一刻开始,数据预取就成为DDR发展的核心因素。

在传统的SDRAM中,每次读取只能操作一个数据。DDR扩大了缓存区,改进了读写设计,将每次读取操作的数据数量由1个变成2个(一般记为2n)。比如同为100MHz,SDRAM在64bit下每秒可以移动0.8GB/s(100×64÷8=800MB/s)的数据,DDR在100MHz、64bit位宽下每秒可移动的数据量就会直接提升到1. 6GB/s(100×64×2÷8=1600MB/s),它的等效频率(等效频率是假定预取依旧是1n的情况下,DDR相当于SDRAM的频率,也叫做名义频率),也就是表面上的数据直接提升了一倍。虽然这看起来很完美,但增加数据预取带来的问题也比较明显——由于读写操作需要准备的数据更多,延迟变得更长。在延迟的影响处于可控范围内、没有让带宽带来增益变成减损之前,继续增大数据预取依旧是DDR发展的重要手段。

因此,在第二代DDR内存也就是DDR2上,数据预取被提高到了4n,在100MHz实际频率、64bit带宽下,DDR2的位宽达到了3.2GB/s(100×64×4÷8=3200MB/s),等效频率是DDR2 400。DDR3则继续提升数据预取至8n,依旧是100MHz,64bit的环境下,DDR3的带宽提升到6.4GB/s(100×64×8÷8=6400MB/s),等效频率是DDR3 800。当然实际发展中由于工艺进步,内存实际的频率并不会总是停滞在100MHz,也出现了诸如133MHz、166MHz、200MHz甚至266MHz的内存,在DDR3上,他们的名义频率分别是DDR3 1066、DDR3 1333、DDR3 1600、DDR3 2133。

在新的DDR4上,数据预取并没有继续增大。原因可能有以下几点:首先,从8n增加到16n的难度比较大,技术设计上存在很大问题;其次,延迟已经开始显示出更为严重的影响了,甚至带宽提高已经难以抵抗延迟带来的负面影响;第三,可能存在比较明显的发热、频率提升的难题。在放弃提升预取值后,DDR4是否就变得乏善可陈了呢?显然不是这样。以GDDR5为例,GDDR5和DDR3在数据预取上都是8n,但是GDDR5采用了特殊的双总线设计,4组Bank Group,双总线对4组Bank Group进行轮流读写操作(相当于在内部组建了个四路并行的模块)。再加上一些专门降低功耗、提高频率的方案,终GDDR5能够达到GDDR5 6000这样惊人的等效频率,DDR4也采用了类似的Bank Group技术,再加上全新的点对点传输、大量的功控制和信号完整性控制技术,依旧呈现出极为优异的发展态势。