英特尔Xeon Phi的x86微异构技术解析

P54C架构,从二十年前的草图起步

既然以P6架构开始的宽发射乱序推测执行架构已经遭遇瓶颈,并且被证明不再适合多核扩展,英特尔的工程师们便选择了P6架构的前代P54C架构作为设计蓝本。乍看之下,这是一个完稿于1995年以前的老旧架构,距今已有近20年。P54C是短流水、顺序执行的简单核心,从性能来看,它与P6相去甚远,可以说是落后了一个时代,甚至没有进入竞技场进行比试的资格。英特尔选择这个架构是不是败笔?

个架构是不是败笔?答案很明确:这非但不是败笔,反倒是一个非常英明的设计决策。英特尔需要一个新的架构与NVIDIA等公司的GPGPU竞争,从本质上来说,这个架构需要容纳数目相当多的核心以提供足够的并行能力,它所需要的技术已经与当下的四核、八核等多核心架构有所不同,因而应该称之为众核架构。在这个众核架构下,选择什么样的核心作为单一基础构建模块便是首要问题。

如果英特尔选择P6或者是更加复杂的高性能核心来组建众核,能耗效率就会不可避免地降低。复杂的高性能x86核心执行串行指令的速度的确很快,但是每一条指令的能耗开销也更大,到了大规模并行的众核时代,如果每条指令的开销还与串行核心一样,这个众核系统就无法交出满意的功耗成绩单。在这一点上,Xeon Phi的设计无疑是果断而正确的,它并非为单线程性能而生,无法将并行的代码交给高性能CPU去完成,推高单线程性能的技术在Xeon Phi身上没有多大用处,它的设计目标是支持多线程并行的众核架构,以并行宽度换取速度。我们不难看出,英特尔也与NVIDIA一样,选择走上了多核心多线程的道路,P54C被加上了硬件四路线程支持,每个核心能够在四个线程间来回切换执行,以重叠存储访问延迟。对于要求吞吐量而不是单线程响应速度的大规模并行计算而言,这是方向正确的一步,但是步幅是否够大,仍不明了。P54C核心目前仅有四线程并行,并且不支持同一个线程在相邻的两个时钟周期内连续发射指令,这就意味着,P54C核心必须喂给至少两个线程才能连续不断地发射指令,四个线程提供的调度空间是否足够隐藏延迟,我们并不清楚。

再看核心内部,P54C为双发射架构,它的执行流水线有两条,为保留奔腾时代的传统,标号分别为U和V。挂载在U流水上的便是XeonPhi架构赖以为生的SIMD执行单元,以及为了提供兼容性而设置的x87浮点处理单元,挂在V流水线上的是负责标量操作的逻辑运算单元,从这一结构看,P54C的确仍然保留了CPU核心的特征,但是又有所不同。传统高性能CPU会在流水线中插入一些缓冲区,以保证某一区域的停顿不会波及整条流水线,这对于单线程性能很重要,但是Xeon Phi架构中的P54C核心则抛弃了这项特征,流水线一旦停顿,则牵一发而动全身。显然这也是为了削减核心复杂度,降低功耗所做的牺牲。几乎退回“石器时代”的串行能力换来了并行能力的突破性进步,U流水下的S IMD执行单元宽度达到了史无前例的512位,是Ivy Bridge的两倍。一个单精度浮点数占据32位宽度,因此这个SIMD单元能够一次执行16个单精度浮点计算。这是有史以来宽的CPU SIMD单元,并且双精度浮点计算速度也达到了单精度的二分之一。这对于部分寄望于使用Xeon Phi来进行科学计算的人来说是个好消息:Intel已经做到半速双精度浮点执行,与NVIDIAFermi架构齐平。

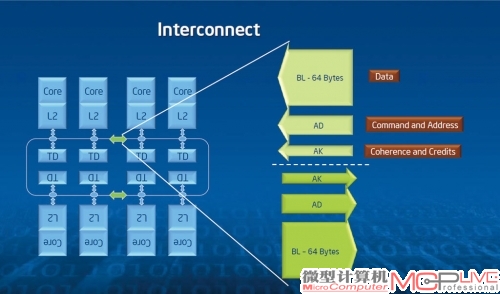

只有一条地址通道和消息通道(橙色点)时,若挂载超过32个核心,系统的性能增长就开始停滞;如果使用两条地址通道和消息通道,就可以一直扩展到超过50个核心。

来自二十年前的P54C架构实现了一步登天。双精度数字占据的存储空间为64位,比单精度多一倍,因此若使用同样的执行资源,双精度计算的速度多只有单精度的一半,但是即便做到半速执行也并不容易,作为对比,GT200的双精度计算速度只有单精度的八分之一,RV870也只有五分之一。NVIDIA和AMD为了抢夺科学计算市场都逐步完善了双精度的半速执行,现在我们看到英特尔也开始强化这方面的表现。单精度浮点的计算精度相对较低,进行一些数值模拟时有更大可能出现误差,如果把代码转变成结果更加精确的双精度执行,在此前的架构上速度就会大幅度降低,因此提高双精度浮点的计算速度是针对科学计算市场的一项重大改进。

除此之外,这个SIMD单元也支持单周期浮点乘加指令,支持向量执行中非常重要的gatte rscatter操作,使用谓词寄存器来处理向量中的条件分支,从这些特性上来看,P54C的改进颇有些向GPGPU靠拢的意味。改进的P54C核心已经具备了GPGPU内部SIMD处理单元的一些特征,英特尔称之为“微异构”,并非没有道理。我们很高兴地看到,作为CPU业界的巨头,英特尔并未固步自封,仍在尝试借鉴GPGPU体系结构中的精华并将之引入自己的众核架构。

缓存与互联,面向未来众核时代

对比GPGPU,Xeon Phi这种基于简单CPU的众核架构对缓存更加重视。每个P54C核心内部都具备32KB的一级指令缓存和32KB一级数据缓存,以及512KB二级缓存。作为对比,NVIDIA Kepler架构的每一个SMX内建4个SIMD处理单元,每个处理单元的宽度允许48个单精度操作,整个SMX允许192个单精度操作,六倍于P54C的宽度,但是这样一个SMX单元才能共享64KB的片上缓存,48K B限制用途的只读常数缓存,以及1.5MB的二级缓存。对缓存的注重并不仅仅来自于对性能的需求,与内存系统在大规模并行计算的前提下,更大的缓存也能够帮助削减功耗。在天河2号这样规模的超级计算机里面,计算能力是很廉价的,真正昂贵的是大规模的数据存储和传输。在同样的功耗限制下传递数据,缓存能够提供更高的带宽。

设计一个双核心到八核心的多核架构,与设计一个60核心的众核架构,需要注重的技术细节有所不同。60核心的架构不是简单堆砌核心就能搭建起来。在少量核心之间切割任务、分工合作、互通消息,是一件相对简单的事情,但是当参与工作的核心数量达到Xeon Phi架构的量级时,性质就不一样了。

从左到右依次为内存、二级缓存和一级缓存,单位功耗下提供的带宽缓存完胜。

Xeon Phi的核心互联网络,由数据通道、地址通道和消息通道组成,双向三通道互联。

想象一下这样的场景:一个多核心处理器接到了计算任务,第一个处理核心将数据复制入自己的内部独立缓存开始处理,完成自己的工作之后,将新结果写回自己的内部独立缓存。第二个核心紧跟着开始自己的计算,这时候问题就来了,刚刚完成的计算结果还保存在第一个核心内部的独立缓存上,第二个核心从内存中取用的数据没有得到来自第一个核心的更新通知,它不能再使用已经失效的旧数据进行计算。新旧数据同时存在时,在多个核心之间保持同步、及时更新数据的过程,被称为保持缓存的一致性。这是影响众核架构是否具备可扩展性的关键因素。显然,第一个核心已经修改的数据必须以某种方式通知其他核心,以确保其后的计算都能及时使用新数据。一种基础架构是,使用总线连接所有处理核心,让修改了数据的处理核心通过总线向其他核心进行广播,其他核心收到总线通知后就将自己缓存中存放的旧数据抛弃,当需要使用新数据时,再通过总线发送广播请求,拥有新数据的核心来应答这个请求。当核心数目较少时,这种监听式架构因为简便易行,容易实现而受到青睐。但是对于Xeon Phi这样的众核架构,使用广播-监听总线的做法就完全不可接受,大量的核心抢用总线会形成严重的竞争,若是在众核架构上部署广播-监听总线来保持缓存一致性,那么它就得具备数百GB/s的惊人带宽,远超当前任何一种芯片内部总线互联系统的承受能力。Xeon Phi必须采用新的互联方式,并且尝试减少泛滥的一致性通信,以降低互联系统的压力,才能真正拥抱众核。

为了达到这样的效果,Xeon Phi的核心之间由环状、双向、三通道的互联系统连接。这三条通道分别为数据通道、地址通道和消息通道。为了在互联系统上一次性传递整个缓存数据块,数据通道达到了惊人的64字节、256位的宽度,与一级缓存的数据块大小吻合,Intel的工程师们为了增强众核架构的可扩展能力,所做的投资可以说是不惜血本。整个缓存一致性协议基于可扩展能力较强的目录系统构建,在每个核心的二级缓存上都额外设立了一个目录,指示其他核心缓存中的数据保存情况。通过探查这个目录,就可以得知其他核心中的数据是否一致,是否能够读写,而目录中的信息依据存储访问动作而在互联系统上相互做出点对点式定向更新,这样一来就大幅减少了无谓的广播消息传递,使得整个互联系统能够挂载更多核心。

即便采用了目录系统,60个核心之间为了保持缓存一致性所带来的通信负担还是太大,每次二级缓存缺失时,计算核心都会在地址通道上生成一个请求,探查目录,如果目录并未指出哪一个核心拥有数据,核心就会再度生成第二个地址,向内存系统请求数据。这样一来,为了获取一个数据块,地址线承受了两倍的压力。仿真结果显示,如果只采用一个地址通道和一个数据通道,那么众核架构增长到超过32个核心时,性能就开始停滞。而加一条地址通道和一个数据通道之后,性能还可以提高,以50个核心为基准,增加通道后的性能可以提升40%,再加上流式储存的优化,在面对某些数组访问较为密集的程序时还可以提升30%。

未来异构,花落谁家?

英特尔XeonPhi众核架构在此之前遭受众多非议,此次助力天河2号登顶Top500榜单可以说是扬眉吐气。众核架构已经证明,自己不但能在超级计算机市场上立足,而且还具备与顶尖级GPU加速系统一决雌雄的能力。但是若要它达到与GPGPU一样的应用规模,可能还需要一段时间才行。抛开纯架构层面的优劣不谈,基于简单x86核心设计众核架构,相对于GPGPU来说有一个显著优点,便是x86的前向兼容性。基于GPGPU的编程需要程序员们额外学习CUDA或者Open CL等通用计算语言,提高了开发门槛;而x86的前向兼容性则意味着此前能够在x86架构上运行的程序也能够在Xeon Phi上运行,或者经过重新编译后运行。这实在是一个致命的诱惑,这意味着,即便GPGPU在基础架构上相对Xeon Phi能领先些许,程序员们也会被x86的大旗给吸引到Xeon Phi的阵营中来,使得GPGPU曲高和寡。愿景虽好,但英特尔试图以这份兼容性作为武器攻击GPGPU,还需跨越一道鸿沟:串行代码的并行化。这是一个世界级难题,SIMD 架构虽然好处多多,但在传统上,SIMD指令大都需要负责性能调优的程序员在代码中手动内联,开发成本较高。编译器只能将比较简单的串行代码实现并行化,尚无力替代人脑。NVIDIA甚至声称,不论现在还是将来,都不可能出现这样一个神奇的编译器,将原本串行的代码自动优化成适合Xeon Phi的并行形式,因此x86前向兼容并不意味着应用可以无缝迁移。程序员永远需要付出劳动,才能编写好的并行代码。GPGPU目前倾向于程序员手动管理缓存,手动处理各个SIMD单元之间可能出现的存储访问交叉,甚至连寄存器压力的优化这种相当底层的细节都暴露给了程序员,程序员能够直接控制许多硬件资源,但是开发难度也较大。Xeon Phi众核架构则实现了硬件缓存一致的存储器系统,解放了程序员管理缓存的压力,但就目前的技术水平来看,这条路还没有辉煌到能够全自动地进行代码并行化。因此从本质上来说,Xeon Phi与GPGPU的较量并非仅仅在于架构上,也在于设计哲学上。两个持有不同价值观的阵营所进行的较量,可能需要相当长的一段时间才能决出胜负。